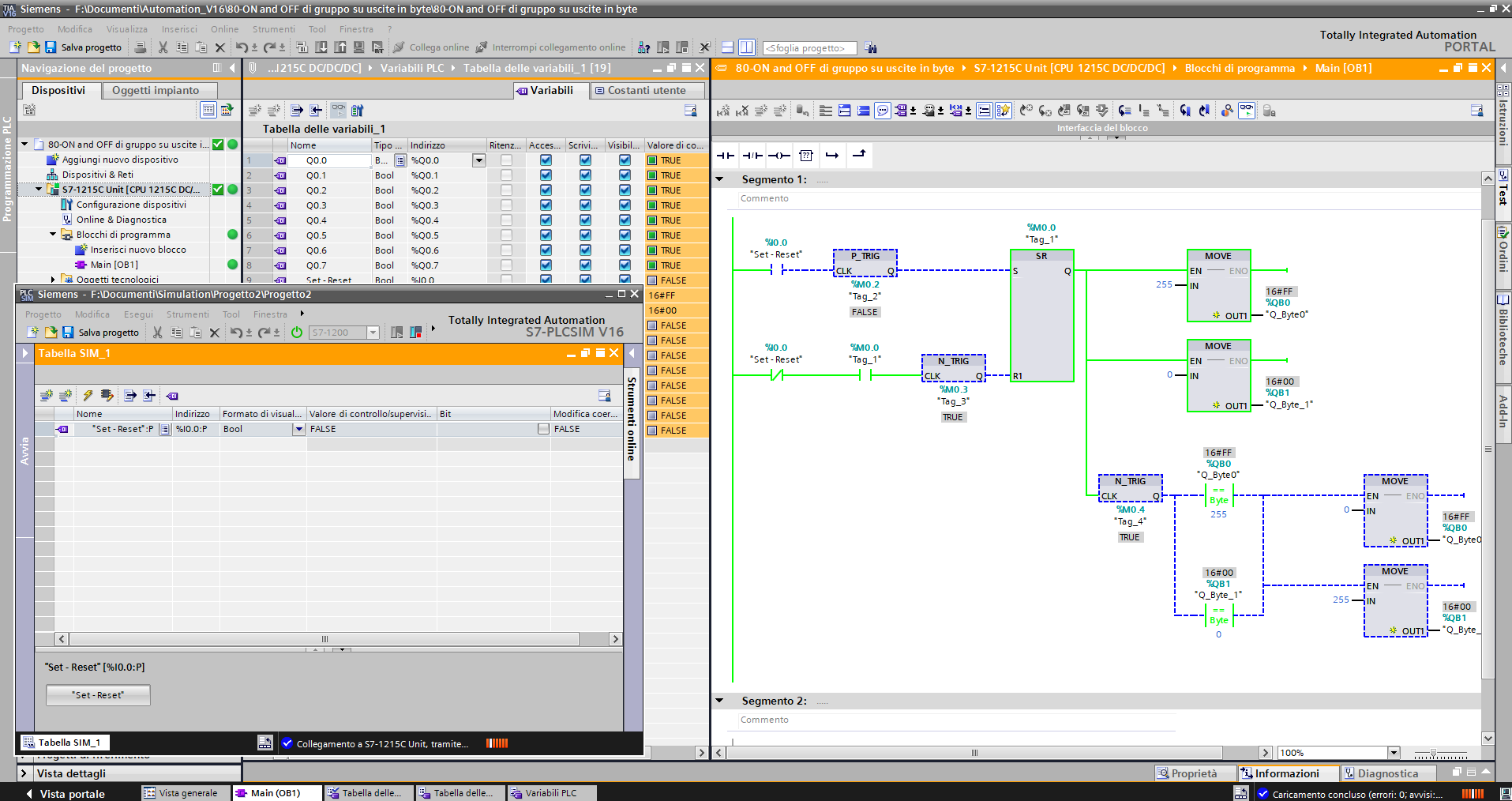

TUTORIAL ESERCIZIO – ON and OFF di gruppo su uscite in byte con SR, P_TRIG, N_TRIG in Tia Portal su S7-1200

In questo esercizio, vediamo come Attivare e Disattvare una serie di Bit in Uscita comandando i Byte, mediante l’uso delle istruzioni SR FlipFlop, N_TRIG e P_TRIG.

Nel corso dell’esercizio vedremo diverse varianti e possibilità di utilizzo.

SR: Flipflop di impostazione/resettaggio

Descrizione

Con l’istruzione “Flipflop di impostazione/resettaggio” si imposta o si resetta il bit di un operando specifico in funzione dello stato del segnale negli ingressi S e R1. Se lo stato di segnale nell’ingresso S è “1” e nell’ingresso R1 è “0”, l’operando specificato viene impostato a “1”. Se lo stato di segnale nell’ingresso S è “0” e nell’ingresso R1 è “1”, l’operando specificato viene resettato a “0”.

L’ingresso R1 prevale sull’ingresso S. Con uno stato di segnale “1” in entrambi gli ingressi S e R1, lo stato di segnale dell’operando indicato viene resettato a “0”.

Se lo stato del segnale degli ingressi S e R1 è “0” l’istruzione non viene eseguita. In questo caso lo stato di segnale dell’operando resta invariato.

Lo stato di segnale attuale dell’operando viene trasferito nell’uscita Q dove può essere letto.

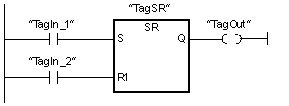

Esempio

Il seguente esempio illustra il funzionamento dell’istruzione:

SR: Flipflop di impostazione/resettaggio

Gli operandi “TagSR” e “TagOut” vengono impostati se vengono soddisfatte le seguenti condizioni:

L’operando “TagIn_1” ha lo stato di segnale “1”.

L’operando “TagIn_2” ha lo stato di segnale “0”.

Gli operandi “TagSR” e “TagOut” vengono resettati se è soddisfatta una delle seguenti condizioni:

L’operando “TagIn_1” ha lo stato di segnale “0” e l’operando “TagIn_2” lo stato di segnale “1”.

Gli operandi “TagIn_1” e “TagIn_2” hanno lo stato di segnale “1”.

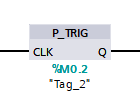

P_TRIG: Interroga il fronte di salita del segnale del RLO

Descrizione

Con l’istruzione “Interroga il fronte di salita del segnale del RLO” si interroga un passaggio da “0” a “1” nello stato di segnale del risultato logico combinatorio (RLO). L’istruzione confronta lo stato di segnale attuale dell’RLO con quello dell’interrogazione precedente memorizzato in un merker del fronte (<Operando>). Se l’istruzione rileva un passaggio da “0” a “1” nell’RLO è presente un fronte di salita del segnale.

Il fronte di salita del segnale viene interrogato a ogni ciclo di esecuzione dell’istruzione. Se viene rilevato un fronte di salita del segnale, l’uscita Q dell’istruzione ha lo stato “1” per un ciclo del programma. In tutti gli altri casi l’uscita ha lo stato di segnale “0”.

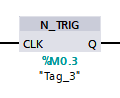

N_TRIG: Interroga il fronte di discesa del segnale del RLO

Descrizione

Con l’istruzione “Interroga il fronte di discesa del segnale del RLO” si interroga un passaggio da “1” a “0” nello stato di segnale del risultato logico combinatorio (RLO). L’istruzione confronta lo stato di segnale attuale dell’RLO con quello dell’interrogazione precedente memorizzato in un merker del fronte (<Operando>). Se l’istruzione rileva un passaggio da “1” a “0” nell’RLO è presente un fronte di discesa del segnale.

Il fronte di discesa del segnale viene interrogato a ogni ciclo di esecuzione dell’istruzione. Se viene rilevato un fronte di discesa del segnale, l’uscita Q dell’istruzione ha lo stato “1” per un ciclo del programma. In tutti gli altri casi lo stato del segnale nell’uscita dell’istruzione è “0”.

Come tutti i miei tutorial, anche questo vi dà le nozioni base per poter poi fantasticare nella realizzazione di tutti i programmi che vi possono venire in mente.

Buon divertimento.

Software necessari:

Download Tia Portal V18: da qui

Ricordo che per essere abilitati al download del software è necessaria una registrazione al sito di supporto Siemens (qui) ed una successiva autorizzazione da parte di Siemens, che può richiedere anche diversi giorni.